- #Whats modelsim pe stand for serial#

- #Whats modelsim pe stand for upgrade#

- #Whats modelsim pe stand for pro#

- #Whats modelsim pe stand for simulator#

The IP core reverts to untethered mode if the device disconnects from the host computer running the Intel ® Quartus ® Prime software.

Untethered-Allows running the design containing the licensed IP for a limited time. If all of the IP cores support unlimited evaluation time, the device does not time-out. If all licensed IP cores in the design support tethered mode, the evaluation time runs until any IP core evaluation expires. The host computer controls the evaluation time by sending a periodic signal to the device via the JTAG port. The Programmer only requires a minimum installation of the Intel ® Quartus ® Prime software, and requires no Intel ® Quartus ® Prime license. #Whats modelsim pe stand for serial#

Tethered mode requires a serial joint test action group (JTAG) cable connected between the JTAG port on your board and the host computer, which is running the Intel ® Quartus ® Prime Programmer for the duration of the hardware evaluation period.

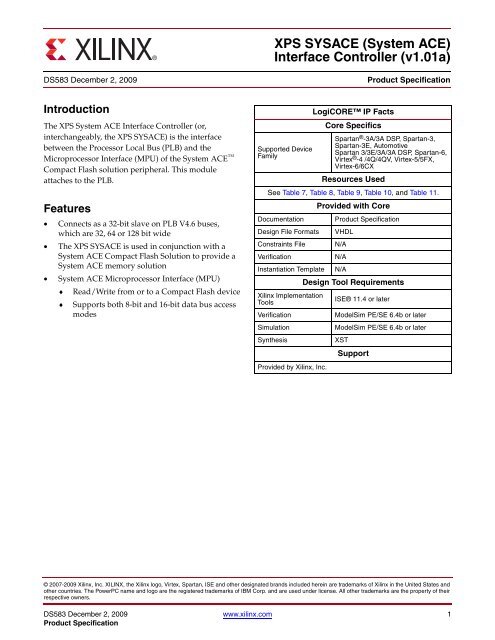

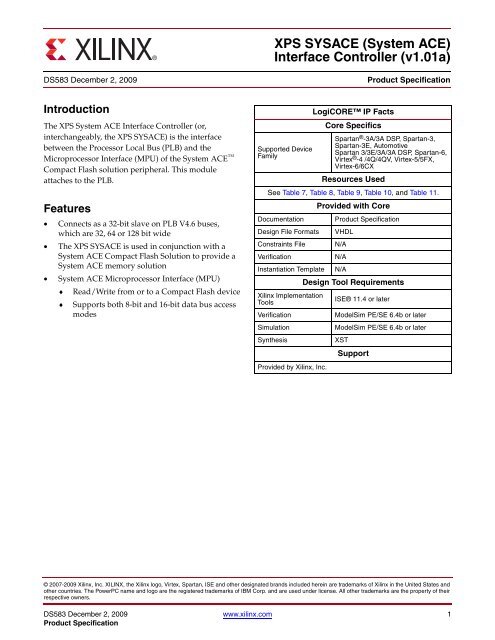

Tethered-Allows running the design containing the licensed Intel ® FPGA IP indefinitely with a connection between your board and the host computer. Intel ® FPGA IP Evaluation Mode supports the following operation modes: Program a device with your IP core and verify your design in hardware. Generate time-limited device programming files for designs that include IP cores. Verify the functionality, size, and speed of the IP core quickly and easily. Simulate the behavior of a licensed Intel ® FPGA IP core in your system. Refer to Creating a System with Platform Designer or Creating a System with Platform Designer (Standard) for information on use of IP in Platform Designer (Standard) and Platform Designer, respectively. The Platform Designer IP Catalog includes exclusive system interconnect, video and image processing, and other system-level IP that are not available in the Intel ® Quartus ® Prime IP Catalog. The IP Catalog is also available in Platform Designer ( View > IP Catalog). Click Sync All System Info to validate a system's generic components against companion files. Click Validate System Integrity to validate a system's generic components against companion files. Click Generate > Generate Example Design to generate an example design (for select cores). Click Generate > Generate Testbench System to generate a testbench system (for select cores).  Use the Details window to view port and parameter descriptions, and click links to documentation. Use the Presets window to apply preset parameter values for specific applications (for select cores). Introduction to Intel FPGA IP Cores Revision History

Use the Details window to view port and parameter descriptions, and click links to documentation. Use the Presets window to apply preset parameter values for specific applications (for select cores). Introduction to Intel FPGA IP Cores Revision History

Introduction to Intel FPGA IP Cores Archives Support for the IEEE 1735 Encryption Standard Generating IP Functional Simulation Models ( Intel Quartus Prime Standard Edition) Setting Up NativeLink Simulation ( Intel Quartus Prime Standard Edition) Using NativeLink Simulation ( Intel Quartus Prime Standard Edition)

#Whats modelsim pe stand for simulator#

Sourcing Synopsys VCS MX Simulator Setup Scripts Sourcing Synopsys VCS Simulator Setup Scripts Sourcing Mentor Graphics ModelSim Simulator Setup Scripts Sourcing Cadence Incisive Simulator Setup Scripts

#Whats modelsim pe stand for pro#

Sourcing Aldec ActiveHDL or Riviera Pro Simulator Setup Scripts Generating a Combined Simulator Setup Script ( Intel Quartus Prime Pro Edition)

#Whats modelsim pe stand for upgrade#

Troubleshooting IP or Platform Designer System Upgrade IP Core Generation Output ( Intel Quartus Prime Standard Edition) Generating IP Cores ( Intel Quartus Prime Standard Edition)

IP Core Generation Output ( Intel Quartus Prime Pro Edition) Generating IP Cores ( Intel Quartus Prime Pro Edition) Installing and Licensing Intel FPGA IP Cores

0 kommentar(er)

0 kommentar(er)